1.简介USB3.0是一种高速,串行,源同步数据传输协议。但是,该数据与通过传输线的原始数据有很大的偏差。

本文从USB3.0的角度分析了弹性缓冲机制,解释了与其他设计的区别,并使用指针控制和握手设计方法将其实现。 2.弹性缓冲功能2.1 USB3.0弹性缓冲范围USB USB3.0的数据传输采用双单工,因此物理层设计为接收和发送2套差分对传输部分。

传输线是承载数据传输的载体。因此,如何正确地从传输线接收数据并将其同步到系统的内部时钟域变得非常关键。

USB3.0中指定的物理层接收部分的结构图如下,其中包括差分接收,时钟数据恢复,串并转换和8B10B解码。 & Nbsp;图1 USB3.0物理层接收部分的结构整个数据从上到下流动,差分输入被差分接收,从差分信号中提取时钟,恢复的时钟用于恢复数据(CDR)。

恢复的数据在接收时钟域中串行并行转换为10位宽的并行数据1,并检测到USB3.0数据包起始标识符(K28.5)。一旦检测到开始标记K28.5,启用符号即有效(符号锁定),并且直到检测到结束符号后,结束符号才有效。

灵活的缓冲将接收到的数据从串行转换为并行,所有接收到的数据和控制工作都在接收时钟域(接收时钟)中进行。因此,弹性缓冲区需要将数据和控制同步到系统时钟域(系统时钟)。

数据被传递到8B10B解码模块,然后传递到系统。 2.2灵活的缓冲容量USB3.0,协议规定允许的时钟精度为-5300ppm至300ppm。

符号时钟频率为2ns或2000ps。在最坏的情况下,每178个符号添加或删除一个SKP,即,每356个符号添加或删除一对SKP(SKP订单集)。

USB3.0中的最长数据包为1052字节,因此在最坏的情况下,最多可以添加或删除8个SKP或4个SKP对,因此弹性缓冲区必须能够缓冲至少8个SKP。 USB3.0协议规定每个SKP指令集是2个连续的SKP符号。

因此,在10B8B解码之前,SKP指令集的运行差异应是互补的。根据计算,弹性缓冲器的缓冲容量为8.本文设计采用正常半满2(normal half full)模式设计弹性缓冲器,因此弹性缓冲容量为16,在正常情况下应是8个数据,其余8个是缓冲区空间,因此称为正常半满。

在正常的半满模式下,必须首先将8个符号写入缓冲区,然后读取使能才能生效,因此存在大约8个时钟的延迟。在通常的半满模式下,当SKP对出现在符号队列中时,只能添加或删除SKP对。

下图显示了恒定半满的输入和输出时序图。 & Nbsp;图2通常为一半的完整输入和输出时序从上图可以看出,rx_valid_out的有效时间晚于rx_valid_in的大约8个时钟沿;而无效时间晚于rx_valid_out大约0到16个时钟沿(取决于时钟精度差异)。

因此,半满时输出数据需要8个时钟延迟。 2.3弹性缓冲区机制弹性缓冲区本质上是一个异步FIFO,可在同时读写时对其进行控制。

普通的半满FIFO的深度为16。它必须首先写入8个有效数据并将其保持在半满状态。

。因此,在正常情况下,FIFO始终处于或接近半满状态。

当读写时钟快或慢时,FIFO中有8个有效数据。 & nbsp;图3通常以相同的速率进行半满读取和写入。

当读取时钟快于写入时钟时,读取的数据多于写入的数据。正常的半满模式可能会导致FIFO中的数据数少于8,甚至可能被读取。

空气。如下图所示,当出现SKP窗口时,FIFO中的有效数据为4,比正常状态小4。

因此,此时,弹性缓冲区应添加4个SKP,以保持FIFO半满以调整时钟。此时,读取指针向前跳转4个间隔,并且当读取指针读取跳转间隔时,SKP添加完成。

& nbsp;图4通常,半满模式的读取速度要快于写入速度。当读取时钟为sl时。

公司: 深圳市捷比信实业有限公司

电话: 0755-29796190

邮箱: ys@jepsun.com

产品经理: 李经理

QQ: 2057469664

地址: 深圳市宝安区翻身路富源大厦1栋7楼

更多资讯

获取最新公司新闻和行业资料。

- 零延迟缓冲器与普通缓冲器的性能对比分析 零延迟缓冲器与普通缓冲器的性能对比分析在现代电子系统设计中,信号完整性与传输延迟是决定系统性能的关键因素。随着高速数字电路的发展,传统的普通缓冲器已逐渐暴露出其在低延迟、高稳定性方面的局限性。相比之下...

- 时钟缓冲器在高速电路设计中的关键价值 时钟缓冲器的功能与系统级意义在复杂的高速数字系统中,时钟信号是整个系统运行的“心跳”。时钟缓冲器作为时钟网络中的核心节点,承担着信号整形、电平转换和负载驱动的重要任务。它不仅改善了时钟信号的上升沿/下降...

- 零延迟缓冲器与低延迟时钟缓冲器的技术原理及应用解析 零延迟缓冲器与低延迟时钟缓冲器的核心技术对比在高速数字系统设计中,时钟信号的完整性与传输延迟直接影响系统的性能与稳定性。零延迟缓冲器(Zero Delay Buffer, ZDB)和低延迟时钟缓冲器(Low Latency Clock Buffer)是两类关键的...

- 如何优化微分时钟信号缓冲器的设计以提升系统稳定性 优化微分时钟信号缓冲器设计的关键策略随着电子系统向更高频率、更低功耗方向发展,微分时钟信号缓冲器的设计面临更大挑战。合理的布局布线、电源管理及器件选型是提升系统稳定性的关键。1. PCB布局与走线优化差分信号...

- 深入理解单端时钟缓冲器的性能指标与选型要点 深入理解单端时钟缓冲器的性能指标与选型要点在高性能电子系统设计中,选择合适的单端时钟缓冲器至关重要。若选型不当,可能导致时钟抖动增加、信号失真甚至系统崩溃。因此,必须从多个维度全面评估其性能参数。一、...

- 零延迟缓冲器工作原理及应用 零延迟缓冲器是一种在信号处理领域广泛应用的技术,它主要用于消除信号传输过程中的延迟问题。在数字信号处理、音频工程以及视频处理等领域中,延迟是一个常见问题,可能导致信号失真或同步问题。零延迟缓冲器通过先...

- 单端时钟缓冲器的工作原理与应用 单端时钟缓冲器是一种在电子电路设计中广泛应用的组件,主要用于提高时钟信号的质量和稳定性。在高速数字系统中,时钟信号是数据传输同步的基础,而单端时钟缓冲器能够有效地解决由于长距离传输或高频率引起的信号衰...

- 如何在高速电路中合理选择零延迟与低延迟时钟缓冲器 高速电路设计中时钟缓冲器的选型策略随着集成电路工作频率不断攀升,时钟信号的延迟与抖动问题日益突出。正确选择零延迟缓冲器或低延迟时钟缓冲器,是确保系统稳定运行的关键环节。一、影响选型的关键参数1. 延迟(Lat...

- 微分时钟信号缓冲器工作原理及应用 微分时钟信号缓冲器是一种在电子工程中广泛应用的组件,主要用于提高时钟信号的质量和稳定性,从而确保数字系统的精确同步。其工作原理基于将输入的时钟信号进行处理,以减少或消除信号传输过程中的失真和噪声,进而...

- PCI Express时钟缓冲器的工作原理与应用解析 PCI Express时钟缓冲器的核心作用PCI Express(PCIe)时钟缓冲器是确保高速数据传输稳定性的关键组件。在现代计算机系统中,PCIe总线用于连接显卡、固态硬盘、网卡等高性能外设。由于这些设备对时序精度要求极高,因此需要精确...

- 单端时钟缓冲器的工作原理与应用解析 单端时钟缓冲器的工作原理与应用解析在现代数字系统设计中,时钟信号的稳定性与传输质量直接影响系统的性能与可靠性。单端时钟缓冲器作为关键组件之一,广泛应用于FPGA、ASIC、微处理器及高速通信设备中。其核心功能是接...

- 微分时钟信号缓冲器的工作原理与应用解析 微分时钟信号缓冲器的核心作用微分时钟信号缓冲器是一种用于高速数字系统中的关键组件,其主要功能是接收输入的时钟信号,并通过差分方式输出,以提高信号完整性、降低噪声干扰并增强抗电磁干扰能力。1. 差分信号传输...

- 时钟缓冲器在现代数字系统中的关键作用 时钟缓冲器的核心功能概述时钟缓冲器是现代数字系统中不可或缺的组成部分,主要作用在于将原始时钟信号复制并分发至多个目标模块,同时保持信号的完整性和时序一致性。无论是单端还是差分架构,时钟缓冲器都承担着“...

- 深入理解时钟缓冲器的类型与选型策略 时钟缓冲器的分类及其应用场景根据工作原理和结构特性,时钟缓冲器可分为多种类型,每种适用于不同的系统需求。正确选择合适的时钟缓冲器,是实现高性能、低功耗系统设计的关键。1. 固定延迟缓冲器(Fixed Delay Buffer)这...

- 时钟缓冲器在数字系统中的作用与应用 时钟缓冲器是数字系统设计中不可或缺的组件之一,它主要负责接收输入时钟信号,并将其放大和分配到多个目的地。在高速数字电路中,时钟信号的质量直接影响到系统的稳定性和性能。因此,时钟缓冲器的作用至关重要,它...

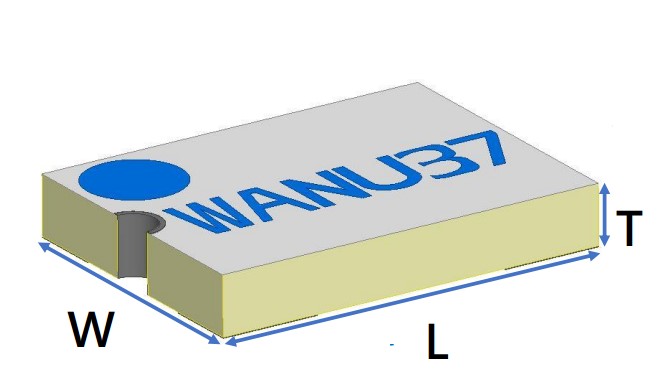

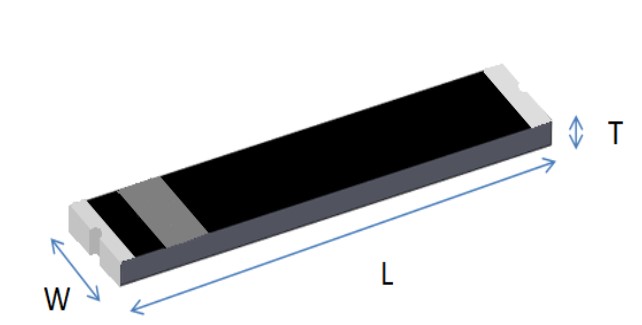

- 光颉viking陶瓷多层片式电感器(CL-S系列):高性能高频应用的理想之选 光颉viking CL-S系列陶瓷多层片式电感器核心优势解析在现代电子设备日益追求小型化、高集成度与高效能的背景下,光颉viking推出的CL-S系列陶瓷多层片式电感器凭借其卓越的电气性能和可靠的稳定性,成为高频电路设计中的首选...

- 时钟缓冲器在数字系统中的关键作用与应用解析 时钟缓冲器的核心功能与重要性时钟缓冲器(Clock Buffer)是现代数字系统中不可或缺的组件,主要用于调节和优化时钟信号的传输质量。在高速集成电路设计中,时钟信号的同步性和稳定性直接影响系统的性能与可靠性。时钟缓...

- 时钟缓冲器在高速数字系统中的关键作用与应用解析 时钟缓冲器在高速数字系统中的核心价值在现代高速数字系统设计中,时钟信号的完整性与稳定性至关重要。时钟缓冲器(Clock Buffer)作为时钟分配网络中的关键组件,承担着信号整形、延迟调节和驱动能力增强的重要功能。1. ...

- 差分时钟缓冲器如何优化系统时序并提升整体性能 差分时钟缓冲器在系统性能优化中的关键角色随着集成电路复杂度的增加,系统时序设计成为制约性能的主要瓶颈。差分时钟缓冲器凭借其卓越的抗噪能力与相位一致性,正成为高性能电子系统不可或缺的组成部分。1. 抗干扰能...

- 直流母线上缓冲电阻的作用 制动电阻很明显是制动作用的。当你的变频器驱动电机高速运行时候,这个时候你需要突然刹车,让电机在较短时间停下来,就要用到刹车电阻了,主要作用是消耗掉电机的能量,转化成热能的形式释放掉。直流母线的问题,首...